# ADSP-2100 FAMILY USER'S MANUAL

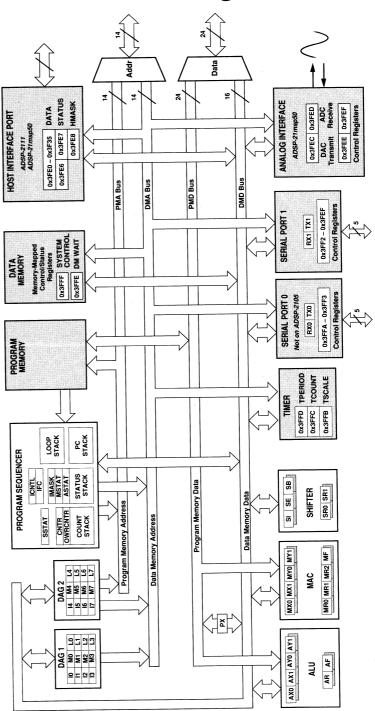

**MEMORY**

SERIAL PORT SERIAL PORT

HOST INTERFACE PORT DSP BASE ARCHITECTURE

ANALOG INTERFACE

**TIMER**

#### ANALOG DEVICES TECHNICAL REFERENCE BOOKS

#### Published by Prentice Hall

Analog-Digital Conversion Handbook

Digital Signal Processing in VLSI

Digital Signal Processing Applications Using the ADSP-2100 Family, Volume 1

Digital Signal Processing Applications Using the ADSP-2100 Family, Volume 2

Digital Signal Processing Laboratory Using the ADSP-2101 Microcomputer

ADSP-2100 Family User's Manual

#### Published by Analog Devices

ADSP-21020 User's Manual ADSP-2106x SHARC User's Manual Digital Signal Processing Applications Using the ADSP-21000 Family

# ADSP-2100 FAMILY USER'S MANUAL

© 1994 by Analog Devices, Inc., Norwood, MA 02062

Published by PTR Prentice-Hall, Inc. A Simon & Schuster Company Englewood Cliffs, New Jersey 07632

The publisher offers discounts on this book when ordered in bulk quantities. For more information write:

PTR Prentice-Hall, Inc. 113 Sylvan Ave. Englewood Cliffs, NJ 07632

Information furnished by Analog Devices, Inc., is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices, Inc., for its use.

Analog Devices, Inc., makes no representation that the interconnection of its circuits as described herein will not infringe on existing or future patent rights, nor do the descriptions contained herein imply the granting of licenses to make, use, or sell equipment constructed in accordance therewith.

Specifications and prices are subject to change without notice.

All rights reserved. No part of this book may be reproduced, in any form or by any means, without permission in writing from the copyright owner.

Printed in the United States of America

10 9 8 7 6 5 4 3

ISBN 0-13-006958-2

Prentice-Hall International (UK) Limited, London Prentice-Hall of Australia Pty. Limited, Sydney Prentice-Hall Canada Inc., Toronto Prentice-Hall Hispanoamericana, S.A., Mexico Prentice-Hall of India Private Limited, New Delhi Prentice-Hall of Japan, Inc., Tokyo Simon & Schuster Asia Pte. Ltd., Singapore Editora Prentice-Hall do Brasil, Ltda., Rio de Janeiro

| CHAI  | PTER 1  | INTRODUCTION                       |    |

|-------|---------|------------------------------------|----|

| 1.1   | OVERVI  | EW                                 |    |

| 1.1.1 | Funct   | tional Units                       |    |

| 1.1.2 | Mem     | ory And System Interface           | 4  |

| 1.1.3 | Instru  | uction Set                         | 4  |

| 1.1.4 |         | Performance                        |    |

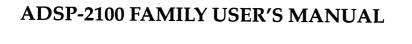

| 1.2   |         | RCHITECTURE                        |    |

| 1.2.1 |         | putational Units                   |    |

| 1.2.2 | Addr    | ess Generators & Program Sequencer | 7  |

| 1.2.3 | Buses   | s                                  | 8  |

| 1.3   | ON-CHI  | IP PERIPHERALS                     | 9  |

| 1.3.1 | Serial  | l Ports                            | 9  |

| 1.3.2 | Time    |                                    |    |

| 1.3.3 | Host    | Interface Port                     | 9  |

| 1.3.4 | Analo   | og Interface                       | 10 |

| 1.4   | ADSP-21 | 100 FAMILY DEVELOPMENT TOOLS       | 10 |

| 1.5   | ORGAN   | IZATION OF THIS MANUAL             | 11 |

| CHAI  | PTER 2  | COMPUTATIONAL UNITS                |    |

| 2.1   | OVERVI  | EW                                 |    |

| 2.1.1 | Binar   | ry String                          | 15 |

| 2.1.2 | Unsig   | gned                               | 15 |

| 2.1.3 | Signe   | ed Numbers: Twos-Complement        | 15 |

| 2.1.4 | Fracti  | ional Representation: 1.15         | 16 |

| 2.1.5 | ALU     | Arithmetic                         | 16 |

| 2.1.6 |         | C Arithmetic                       |    |

| 2.1.7 | Shifte  | er Arithmetic                      | 17 |

| 2.1.8 | Sumr    | mary                               | 18 |

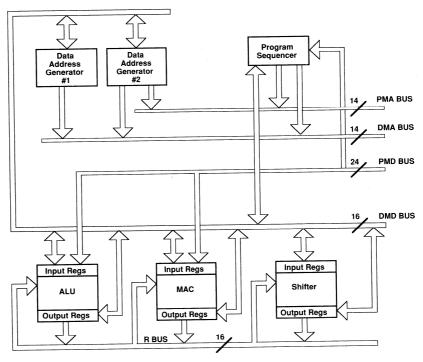

| 2.2   | ARITHM  | METÍC/LOGIC UNIT (ALU)             | 19 |

| 2.2.1 | ALU     | Block Diagram Discussion           | 19 |

| 2.2.2 |         | lard Functions                     |    |

| 2.2.3 | ALU     | Input/Output Registers             | 22 |

| 2.2.4                                                                                                                                               | M. Miliana di di da Cara dellitra                                                                                                                                                                                                                                                                                                                                                                                                            | 22                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

|                                                                                                                                                     | Multiprecision Capability                                                                                                                                                                                                                                                                                                                                                                                                                    | 22                                                                               |

| 2.2.5                                                                                                                                               | ALU Saturation Mode                                                                                                                                                                                                                                                                                                                                                                                                                          | 22                                                                               |

| 2.2.6                                                                                                                                               | ALU Overflow Latch Mode                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                  |

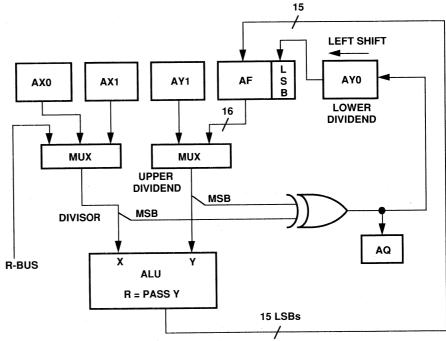

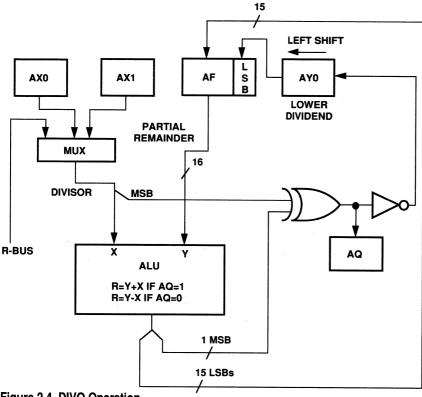

| 2.2.7                                                                                                                                               | Division                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                  |

| 2.2.8                                                                                                                                               | ALU Status                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                  |

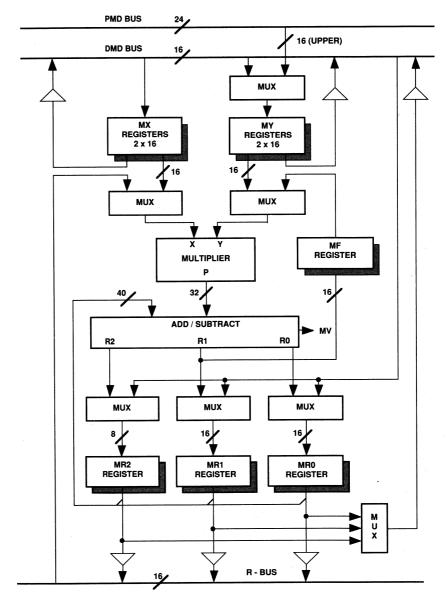

| 2.3                                                                                                                                                 | MULTIPLIER/ACCUMULATOR (MAC)                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                  |

| 2.3.1                                                                                                                                               | MAC Block Diagram Discussion                                                                                                                                                                                                                                                                                                                                                                                                                 | 27                                                                               |

| 2.3.2                                                                                                                                               | MAC Operations                                                                                                                                                                                                                                                                                                                                                                                                                               | 30                                                                               |

| 2.3.2.1                                                                                                                                             | Standard Functions                                                                                                                                                                                                                                                                                                                                                                                                                           | 30                                                                               |

| 2.3.2.2                                                                                                                                             | Input Formats                                                                                                                                                                                                                                                                                                                                                                                                                                | 32                                                                               |

| 2.3.2.3                                                                                                                                             | MAC Input/Output Registers                                                                                                                                                                                                                                                                                                                                                                                                                   | 32                                                                               |

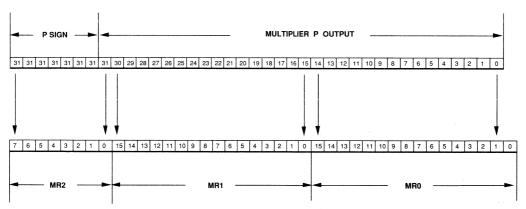

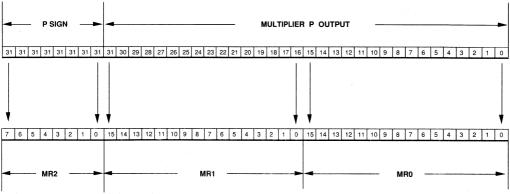

| 2.3.2.4                                                                                                                                             | MR Register Operation                                                                                                                                                                                                                                                                                                                                                                                                                        | 33                                                                               |

| 2.3.2.5                                                                                                                                             | MR Register Operation                                                                                                                                                                                                                                                                                                                                                                                                                        | 33                                                                               |

| 2.3.2.6                                                                                                                                             | Rounding Mode                                                                                                                                                                                                                                                                                                                                                                                                                                | 34                                                                               |

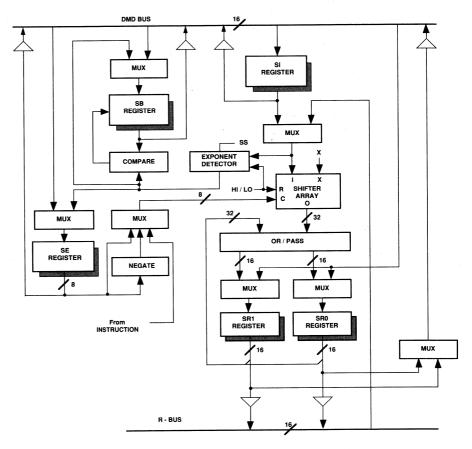

| 2.4                                                                                                                                                 | BARREL SHIFTER                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                  |

| 2.4.1                                                                                                                                               | Shifter Block Diagram Discussion                                                                                                                                                                                                                                                                                                                                                                                                             | 35                                                                               |

| 2.4.2                                                                                                                                               | Shifter Operations                                                                                                                                                                                                                                                                                                                                                                                                                           | 40                                                                               |

| 2.4.2.1                                                                                                                                             | Shifter Input/Output Registers                                                                                                                                                                                                                                                                                                                                                                                                               | 42                                                                               |

|                                                                                                                                                     | Devive Plack Evenent                                                                                                                                                                                                                                                                                                                                                                                                                         | 12                                                                               |

| 2.4.2.2                                                                                                                                             | Derive Block Exponent Immediate Shifts                                                                                                                                                                                                                                                                                                                                                                                                       | 12                                                                               |

| 2.4.2.3                                                                                                                                             | Immediate Shirts                                                                                                                                                                                                                                                                                                                                                                                                                             | 45                                                                               |

| 2.4.2.4 2.4.2.5                                                                                                                                     | Denormalize<br>Normalize                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                  |

| 2.4.2.0                                                                                                                                             | 1 VOITIMIZE                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                  |

|                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                  |

|                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                  |

| СНАР                                                                                                                                                | FFR 3 PROGRAM CONTROL                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                  |

| CHAP                                                                                                                                                | TER 3 PROGRAM CONTROL                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                  |

|                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                              | 51                                                                               |

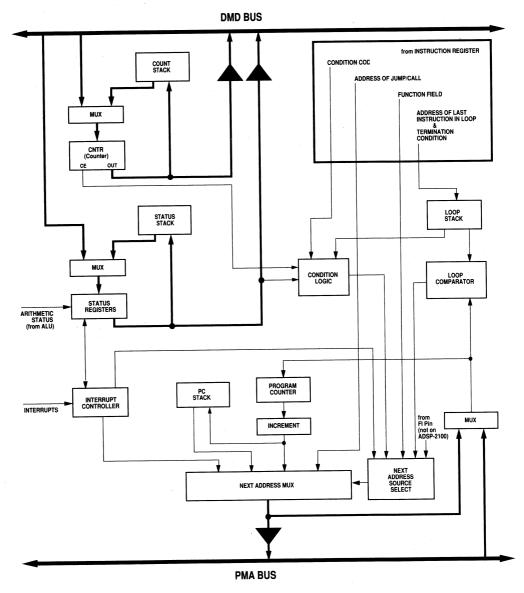

| 3.1                                                                                                                                                 | OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                  |

| 3.1<br>3.2                                                                                                                                          | OVERVIEWPROGRAM SEQUENCER                                                                                                                                                                                                                                                                                                                                                                                                                    | 51                                                                               |

| 3.1<br>3.2<br>3.2.1                                                                                                                                 | OVERVIEWPROGRAM SEQUENCERNext Address Select Logic                                                                                                                                                                                                                                                                                                                                                                                           | 51<br>53                                                                         |

| 3.1<br>3.2<br>3.2.1<br>3.2.2                                                                                                                        | OVERVIEW PROGRAM SEQUENCER Next Address Select Logic Program Counter And PC Stack                                                                                                                                                                                                                                                                                                                                                            | 51<br>53<br>54                                                                   |

| 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3                                                                                                               | OVERVIEW PROGRAM SEQUENCER Next Address Select Logic Program Counter And PC Stack Loop Counter And Stack                                                                                                                                                                                                                                                                                                                                     | 51<br>53<br>54                                                                   |

| 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4                                                                                                      | OVERVIEW PROGRAM SEQUENCER Next Address Select Logic Program Counter And PC Stack Loop Counter And Stack Loop Comparator And Stack                                                                                                                                                                                                                                                                                                           | 51<br>53<br>54<br>55                                                             |

| 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.3                                                                                               | OVERVIEW PROGRAM SEQUENCER Next Address Select Logic Program Counter And PC Stack Loop Counter And Stack Loop Comparator And Stack PROGRAM CONTROL INSTRUCTIONS                                                                                                                                                                                                                                                                              | 51<br>53<br>54<br>55<br>55                                                       |

| 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.3<br>3.3.1                                                                                      | OVERVIEW PROGRAM SEQUENCER Next Address Select Logic Program Counter And PC Stack Loop Counter And Stack Loop Comparator And Stack PROGRAM CONTROL INSTRUCTIONS JUMP Instruction                                                                                                                                                                                                                                                             | 51<br>53<br>54<br>55<br>55<br>58                                                 |

| 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.3<br>3.3.1<br>3.3.1.1                                                                           | OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                     | 51<br>53<br>54<br>55<br>58<br>58                                                 |

| 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.3<br>3.3.1<br>3.3.1.1<br>3.3.2                                                                  | OVERVIEW PROGRAM SEQUENCER Next Address Select Logic Program Counter And PC Stack Loop Counter And Stack Loop Comparator And Stack PROGRAM CONTROL INSTRUCTIONS JUMP Instruction Register Indirect JUMPs CALL Instruction                                                                                                                                                                                                                    | 51<br>54<br>54<br>55<br>58<br>58<br>58                                           |

| 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.3<br>3.3.1<br>3.3.1.1<br>3.3.2<br>3.3.3                                                         | OVERVIEW PROGRAM SEQUENCER Next Address Select Logic Program Counter And PC Stack Loop Counter And Stack Loop Comparator And Stack PROGRAM CONTROL INSTRUCTIONS JUMP Instruction Register Indirect JUMPs CALL Instruction DO UNTIL Loops                                                                                                                                                                                                     | 51<br>54<br>55<br>58<br>58<br>58<br>58                                           |

| 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.3<br>3.3.1<br>3.3.1.1<br>3.3.2                                                                  | OVERVIEW PROGRAM SEQUENCER Next Address Select Logic Program Counter And PC Stack Loop Counter And Stack Loop Comparator And Stack PROGRAM CONTROL INSTRUCTIONS JUMP Instruction Register Indirect JUMPs CALL Instruction DO UNTIL Loops                                                                                                                                                                                                     | 51<br>54<br>55<br>58<br>58<br>58<br>58                                           |

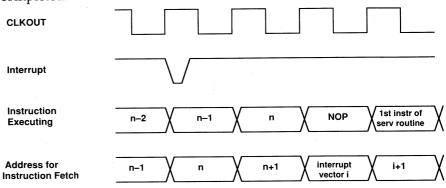

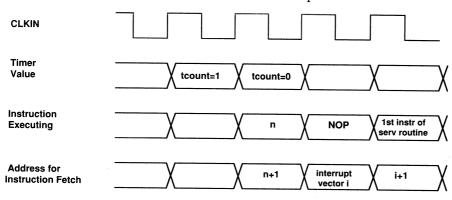

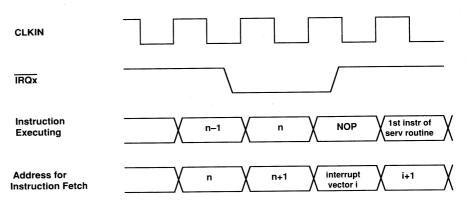

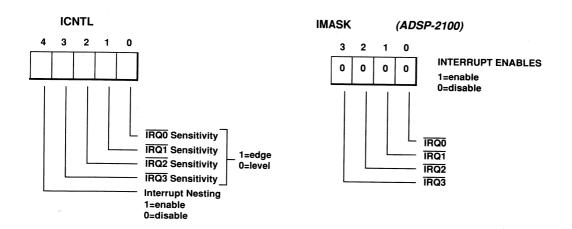

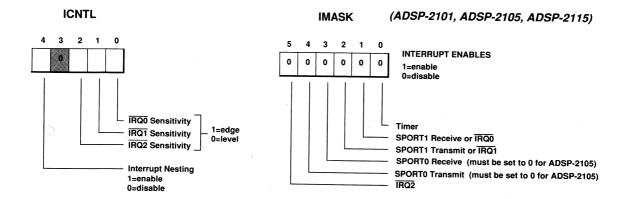

| 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.3<br>3.3.1<br>3.3.1.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.4                                         | OVERVIEW PROGRAM SEQUENCER Next Address Select Logic Program Counter And PC Stack Loop Counter And Stack Loop Comparator And Stack PROGRAM CONTROL INSTRUCTIONS JUMP Instruction Register Indirect JUMPs CALL Instruction DO UNTIL Loops IDLE Instruction INTERRUPT CONTROLLER                                                                                                                                                               | 51<br>53<br>54<br>55<br>58<br>58<br>58<br>58<br>59<br>60                         |

| 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.3<br>3.3.1<br>3.3.1.1<br>3.3.2<br>3.3.3<br>3.3.4                                                | OVERVIEW PROGRAM SEQUENCER Next Address Select Logic Program Counter And PC Stack Loop Counter And Stack Loop Comparator And Stack PROGRAM CONTROL INSTRUCTIONS JUMP Instruction Register Indirect JUMPs CALL Instruction DO UNTIL Loops IDLE Instruction INTERRUPT CONTROLLER Interrupt Servicing Sequence                                                                                                                                  | 51<br>53<br>54<br>55<br>58<br>58<br>58<br>58<br>58<br>59<br>60                   |

| 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.3<br>3.3.1<br>3.3.1.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.4                                         | OVERVIEW PROGRAM SEQUENCER Next Address Select Logic Program Counter And PC Stack Loop Counter And Stack Loop Comparator And Stack PROGRAM CONTROL INSTRUCTIONS JUMP Instruction Register Indirect JUMPs CALL Instruction DO UNTIL Loops IDLE Instruction INTERRUPT CONTROLLER Interrupt Servicing Sequence Configuring Interrupts                                                                                                           | 51<br>53<br>54<br>55<br>58<br>58<br>58<br>58<br>58<br>60<br>60                   |

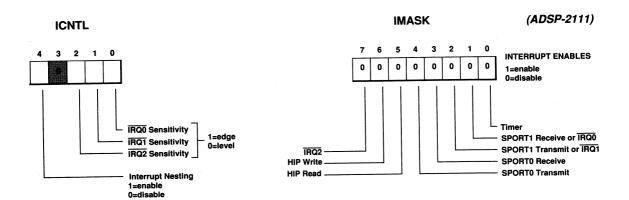

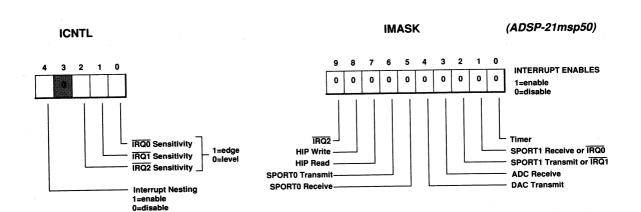

| 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.3<br>3.3.1<br>3.3.1.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.4<br>3.4                                  | OVERVIEW PROGRAM SEQUENCER Next Address Select Logic Program Counter And PC Stack Loop Counter And Stack Loop Comparator And Stack PROGRAM CONTROL INSTRUCTIONS JUMP Instruction Register Indirect JUMPs CALL Instruction DO UNTIL Loops IDLE Instruction INTERRUPT CONTROLLER Interrupt Servicing Sequence Configuring Interrupts Interrupt Control Register (ICNTL)                                                                        | 51<br>53<br>54<br>55<br>58<br>58<br>58<br>58<br>60<br>60<br>63                   |

| 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.3<br>3.3.1<br>3.3.1.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.4<br>3.4.1<br>3.4.2                       | OVERVIEW PROGRAM SEQUENCER Next Address Select Logic Program Counter And PC Stack Loop Counter And Stack Loop Comparator And Stack PROGRAM CONTROL INSTRUCTIONS JUMP Instruction Register Indirect JUMPs CALL Instruction DO UNTIL Loops IDLE Instruction INTERRUPT CONTROLLER Interrupt Servicing Sequence Configuring Interrupts Interrupt Control Register (ICNTL) Interrupt Mask Register (IMASK)                                        | 51<br>53<br>54<br>55<br>58<br>58<br>58<br>58<br>60<br>60<br>63<br>63             |

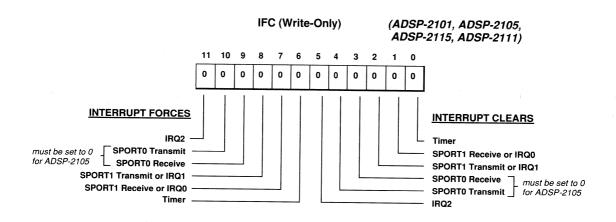

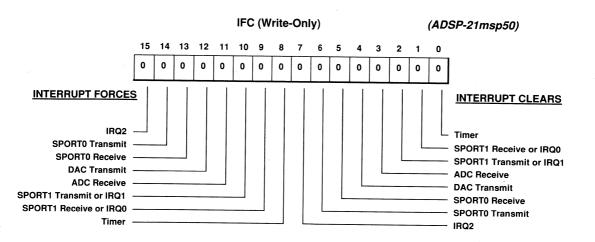

| 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.3<br>3.3.1<br>3.3.1.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.4<br>3.4.1<br>3.4.2<br>3.4.2.1            | OVERVIEW PROGRAM SEQUENCER Next Address Select Logic Program Counter And PC Stack Loop Counter And Stack Loop Comparator And Stack PROGRAM CONTROL INSTRUCTIONS JUMP Instruction Register Indirect JUMPs CALL Instruction DO UNTIL Loops IDLE Instruction INTERRUPT CONTROLLER Interrupt Servicing Sequence Configuring Interrupts Interrupt Control Register (ICNTL) Interrupt Mask Register (IMASK) Interrupt Force & Clear Register (IFC) | 51<br>53<br>54<br>55<br>58<br>58<br>58<br>58<br>60<br>60<br>63<br>63<br>65<br>65 |

| 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.3<br>3.3.1<br>3.3.1.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.4<br>3.4.1<br>3.4.2<br>3.4.2.1<br>3.4.2.2 | OVERVIEW PROGRAM SEQUENCER Next Address Select Logic Program Counter And PC Stack Loop Counter And Stack Loop Comparator And Stack PROGRAM CONTROL INSTRUCTIONS JUMP Instruction Register Indirect JUMPs CALL Instruction DO UNTIL Loops IDLE Instruction INTERRUPT CONTROLLER Interrupt Servicing Sequence Configuring Interrupts Interrupt Control Register (ICNTL)                                                                        | 51<br>53<br>54<br>55<br>58<br>58<br>58<br>58<br>60<br>60<br>63<br>63<br>65<br>65 |

| 3.5     | STATUS REGISTER                                                                                                                                                                                                                  | S & STATUS STACK           | 70        |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------|

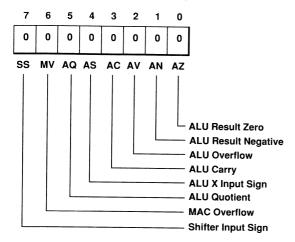

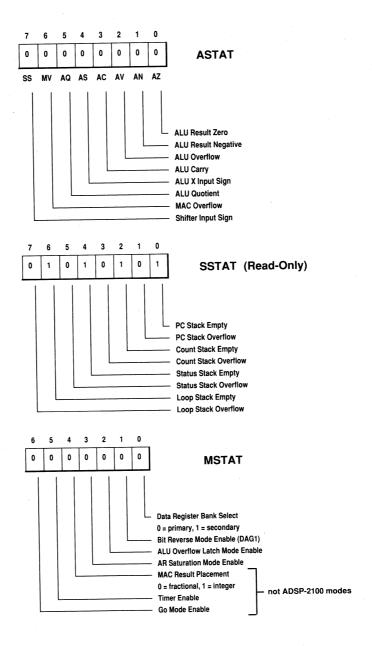

| 3.5.1   | Arithmetic Status                                                                                                                                                                                                                | s Register (ASTAT)         | 71        |

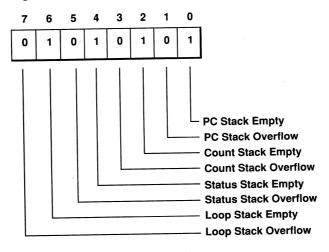

| 3.5.2   | Stack Status Regi                                                                                                                                                                                                                | ister (SSTAT)              | 70        |

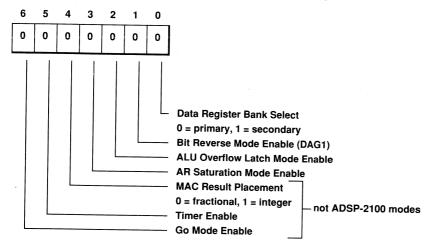

| 3.5.3   | Mode Status Reg                                                                                                                                                                                                                  | gister (MSTAT)             | 73        |

| 3.6     | CONDITIONAL IN                                                                                                                                                                                                                   | STRUCTIONS                 | 75        |

| 3.7     | ADSP-2100 INSTRU                                                                                                                                                                                                                 | JCTION CACHE               | 76        |

| 3.7.1   | Cache Memory C                                                                                                                                                                                                                   | Operation                  | 76        |

| 3.7.2   | Cache Memory N                                                                                                                                                                                                                   | Monitor                    | 77        |

| 3.7.3   | Programmers' G                                                                                                                                                                                                                   | uidelines For Cache Memory | 77        |

| 3.7.4   | Cache Memory F                                                                                                                                                                                                                   | Example                    | 79        |

|         |                                                                                                                                                                                                                                  | zampie                     | ····· / C |

|         | en de la companya de<br>La companya de la co |                            |           |

| CHAP    | TER 4 DATA                                                                                                                                                                                                                       | TRANSFER                   |           |

| 4.1     | OVERVIEW                                                                                                                                                                                                                         |                            | 81        |

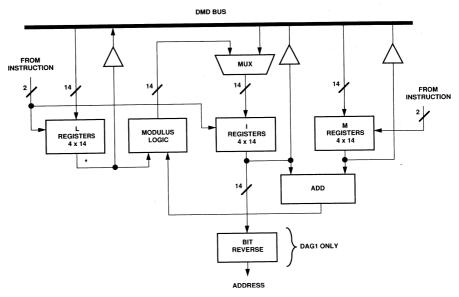

| 4.2     | DATA ADDRESS G                                                                                                                                                                                                                   | ENERATORS (DAGS)           | 81        |

| 4.2.1   | DAG Architectur                                                                                                                                                                                                                  | re                         | 81        |

| 4.2.2   | Modulo Address                                                                                                                                                                                                                   | sing                       | 83        |

| 4.2.3   | Calculating The I                                                                                                                                                                                                                | Base Address               | 84        |

| 4.2.3.1 | Circular Buffe                                                                                                                                                                                                                   | er Base Address Example 1  | 84        |

| 4.2.3.2 | Circular Buffe                                                                                                                                                                                                                   | er Base Address Example 2  | 84        |

| 4.2.3.3 | Circular Butte                                                                                                                                                                                                                   | er Operation Example 1     | 95        |

| 4.2.3.4 | Circular Buffe                                                                                                                                                                                                                   | er Operation Example 2     | 85        |

| 4.2.4   | bit-Keverse Addr                                                                                                                                                                                                                 | ressing                    | 85        |

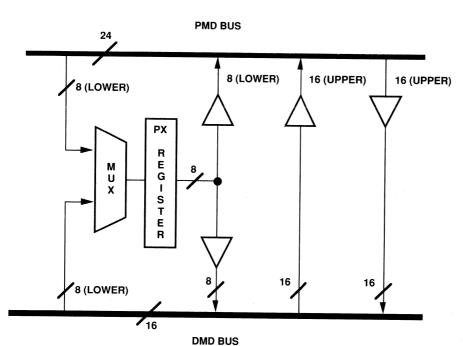

| 4.3     | PMD-DMD BUS EXC                                                                                                                                                                                                                  | CHANGE                     | 86        |

| 4.3.1   | PMD-DMD Block                                                                                                                                                                                                                    | k Diagram Discussion       | 86        |

|         |                                                                                                                                                                                                                                  |                            |           |

| CHAP    | ΓER 5 SERIAL                                                                                                                                                                                                                     | L PORTS                    |           |

| 5.1     | OVERVIEW                                                                                                                                                                                                                         |                            | 80        |

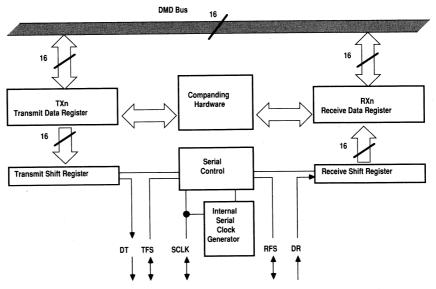

| 5.2     | BASIC SPORT DESC                                                                                                                                                                                                                 | CRIPTION                   | 90        |

| 5.2.1   | Interrupts                                                                                                                                                                                                                       |                            | وی        |

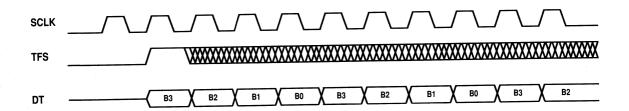

| 5.2.2   | SPORT Operation                                                                                                                                                                                                                  | n                          | 92        |

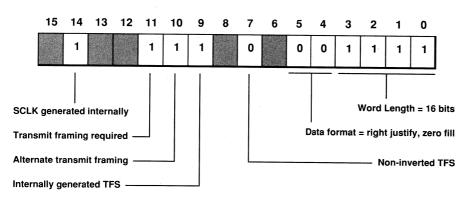

| 5.3     | SPORT PROGRAMA                                                                                                                                                                                                                   | MING                       | 92        |

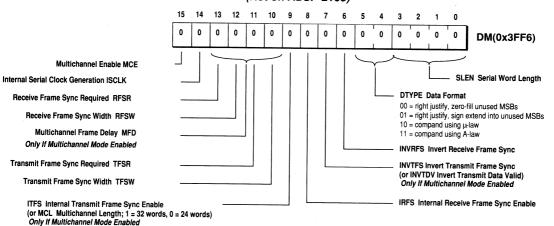

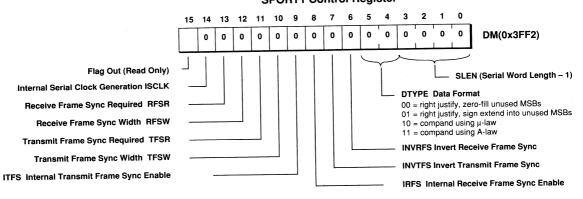

| 5.3.1   | SPORT Configura                                                                                                                                                                                                                  | ation                      | 92        |

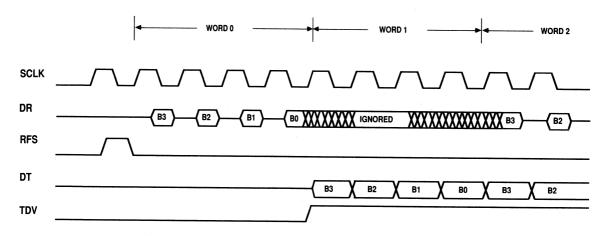

| 5.3.2   | Receiving And Tr                                                                                                                                                                                                                 | ransmitting Data           | Ω1        |

| 5.4     | SPORT ENABLE                                                                                                                                                                                                                     |                            |           |

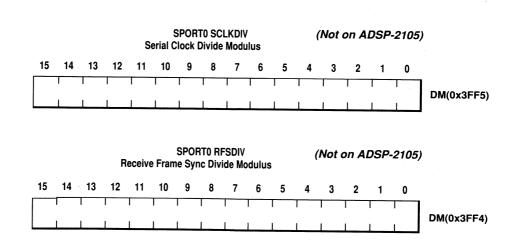

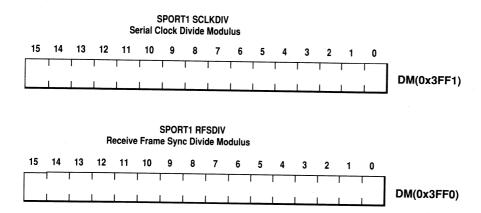

| 5.5     | SERIAL CLOCKS                                                                                                                                                                                                                    |                            | 93        |

| 5.6     | WORD LENGTH                                                                                                                                                                                                                      |                            | 90        |

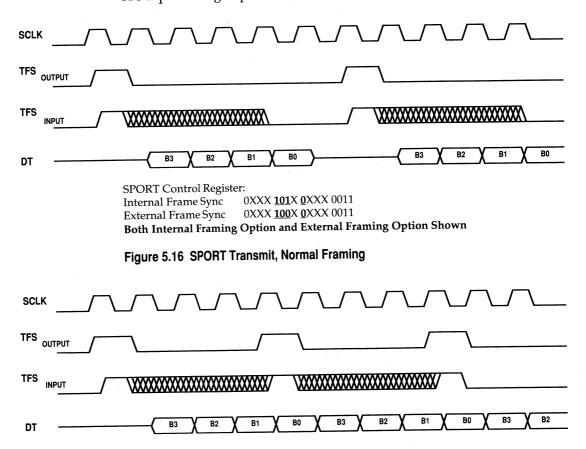

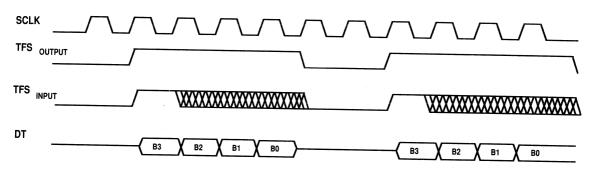

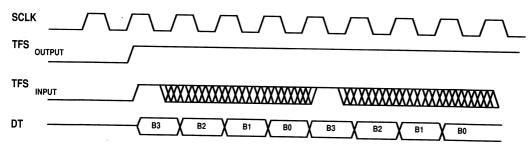

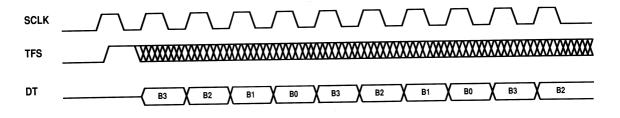

| 5.7     | WORD FRAMING C                                                                                                                                                                                                                   | OPTIONS                    |           |

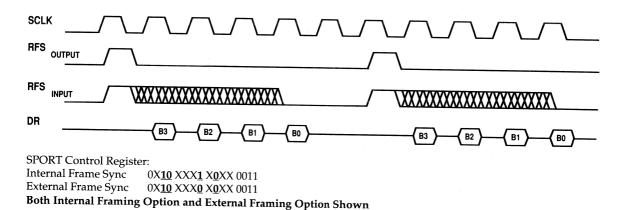

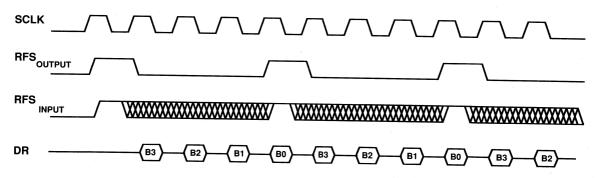

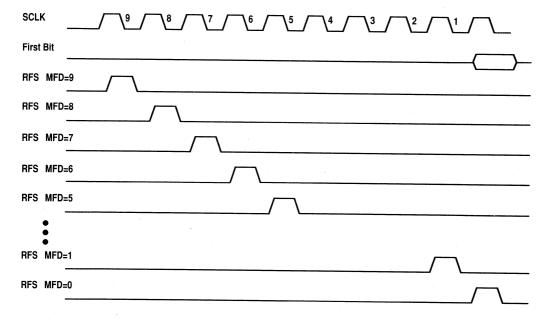

| 5.7.1   | Frame Synchronia                                                                                                                                                                                                                 | zation                     |           |

| 5.7.2   | Frame Sync Signa                                                                                                                                                                                                                 | al Source                  |           |

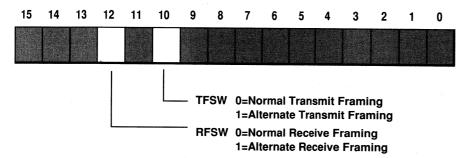

| 5.7.3   | Normal And Alte                                                                                                                                                                                                                  | ernate Framing Modes       |           |

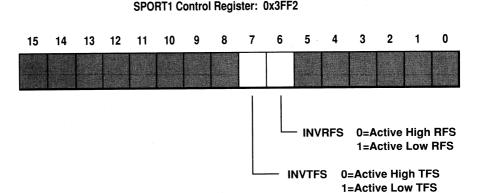

| 5.7.4   | Active High Or A                                                                                                                                                                                                                 | active Low                 | 107       |

|         |                                                                                                                                                                                                                                  |                            | 102       |

| 5.8      | CONFIGURATION EXAMPLE10                                       | )3  |

|----------|---------------------------------------------------------------|-----|

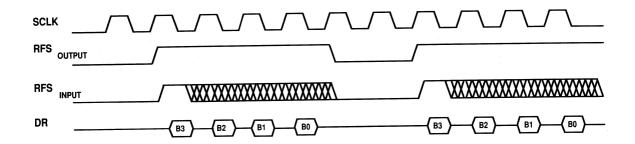

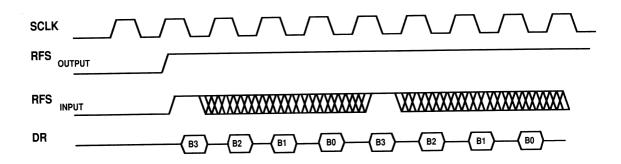

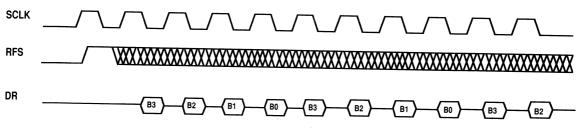

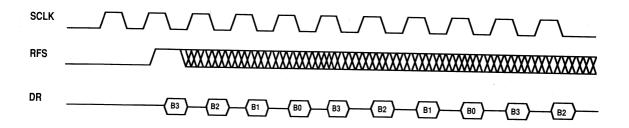

| 5.9      | TIMING EXAMPLES10                                             | )4  |

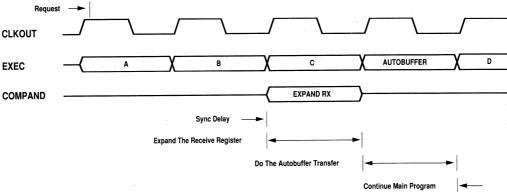

| 5.10     | COMPANDING AND DATA FORMAT1                                   | 11  |

| 5.10.1   | Companding Operation Example1                                 | 12  |

| 5.10.2   | Contention For Companding Hardware1                           | 13  |

| 5.10.3   | Companding Internal Data                                      | 13  |

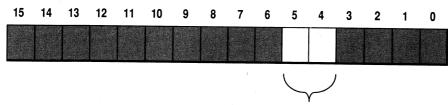

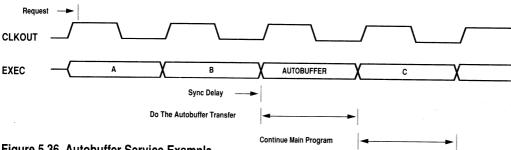

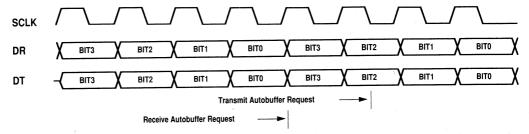

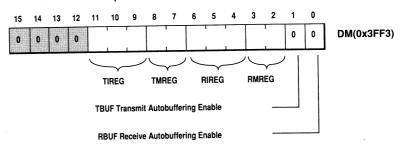

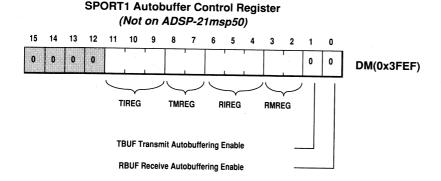

| 5.11     | AUTOBUFFERING                                                 | 14  |

| 5.11.1   | Autobuffering Control Register1                               | 15  |

| 5.11.2   | Autobuffering Example1                                        | 16  |

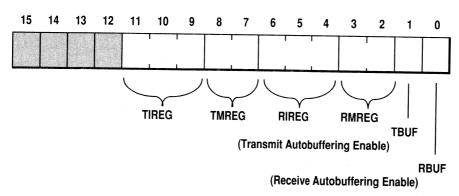

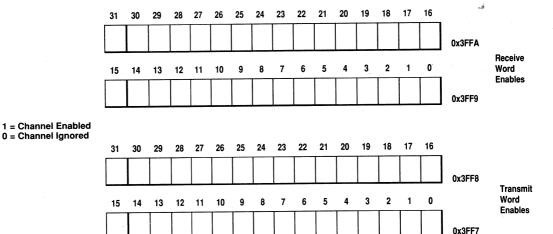

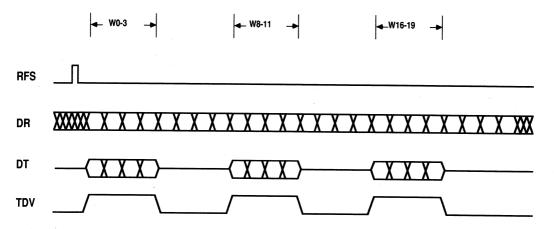

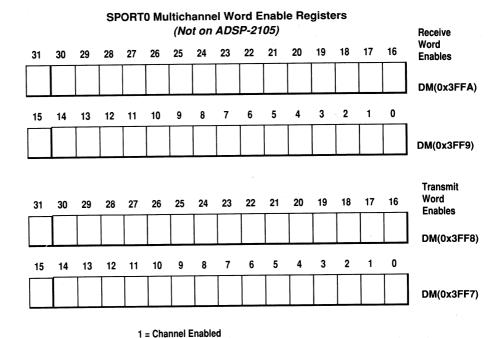

| 5.12     | MULTICHANNEL FUNCTION                                         | 18  |

| 5.12.1   | Multichannel Setup1                                           | 18  |

| 5.12.2   | Multichannel Operation                                        | 20  |

| 5.13     | SPORT TIMING CONSIDERATIONS12                                 | 22  |

| 5.13.1   | Companding Delay1                                             | 22  |

| 5.13.2   | Clock Synchronization Delay                                   | 22  |

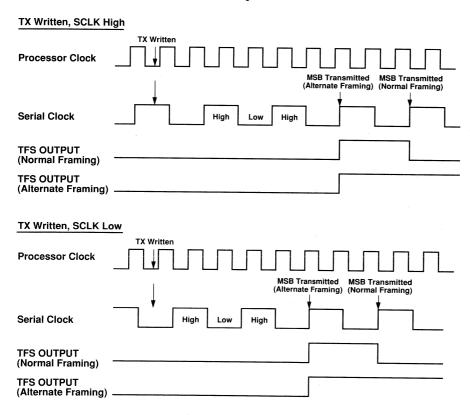

| 5.13.2.1 | Startup Timing13                                              | 22  |

| 5.13.3   | Internally Generated Frame Sync Timing                        | 22  |

| 5.13.4   | Transmit Interrupt Timing                                     | 24  |

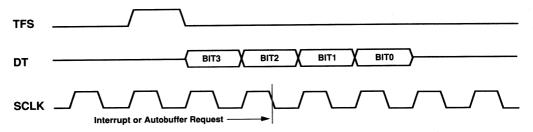

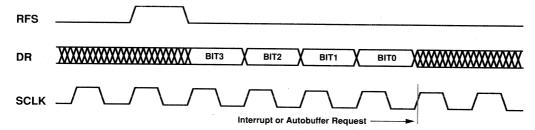

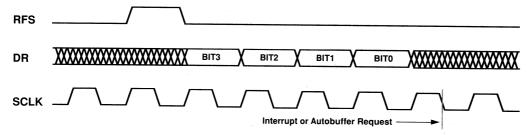

| 5.13.5   | Receive Interrupt Timing1                                     | 24  |

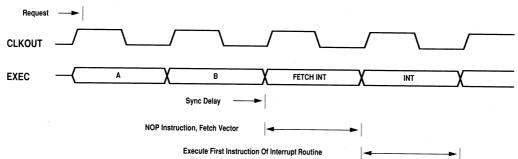

| 5.13.6   | Interrupt And Autobuffer Synchronization1                     | 26  |

| 5.13.7   | Instruction Completion Latencies1                             | 26  |

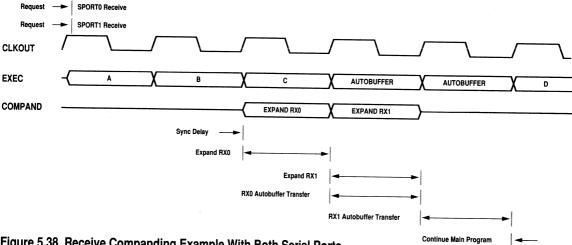

| 5.13.8   | Interrupt And Autobuffer Service Example1                     | 27  |

| 5.13.9   | Receive Companding Latency1                                   | 28  |

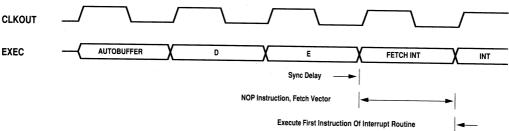

| 5.13.10  | Interrupts With Autobuffering Enabled1                        | 29  |

| 5.13.11  | Interrupts With Autobuffering Enabled1 Unusual Complications1 | 30  |

|          |                                                               |     |

|          |                                                               |     |

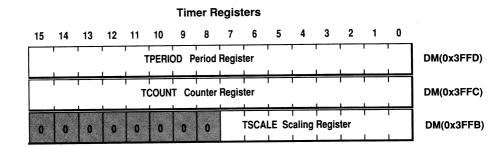

| CHAP'    | TER 6 TIMER                                                   |     |

|          |                                                               | 21  |

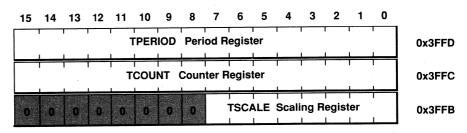

| 6.1      | OVERVIEW1                                                     | 31  |

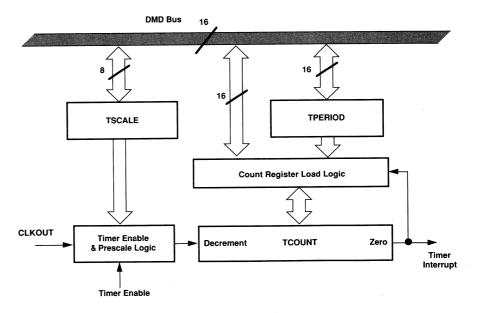

| 6.2      | TIMER ARCHITECTURE                                            |     |

| 6.3      | RESOLUTION1                                                   | 33  |

| 6.4      | TIMER OPERATION1                                              | .33 |

| CHAP    | TER 7      | HOST INTERFACE PORT (ADSP-2111, ADSP-       | -21msp50A)      |

|---------|------------|---------------------------------------------|-----------------|

| 7.1     | OVERVIEV   | V                                           | 105             |

| 7.2     | HIP PIN SI | JMMARY                                      | 133             |

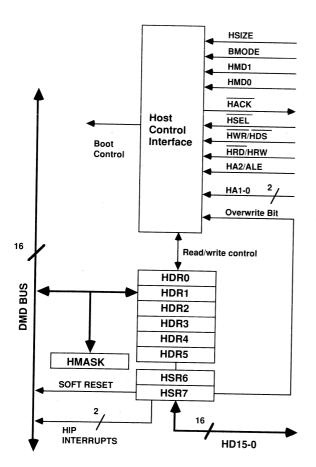

| 7.3     | HIP FUNC   | TIONAL DESCRIPTION                          | 130             |

| 7.4     | HIP OPERA  | ATION                                       | 130             |

| 7.4.1   | Polled C   | Operation                                   | 140<br>141      |

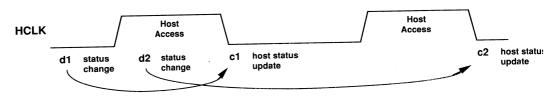

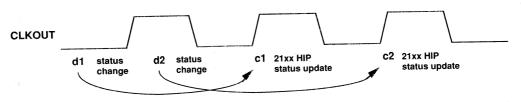

| 7.4.1.1 | HIP        | Status Synchronization                      | 141             |

| 7.4.2   | Interrur   | ott-Driven Operation                        | 142             |

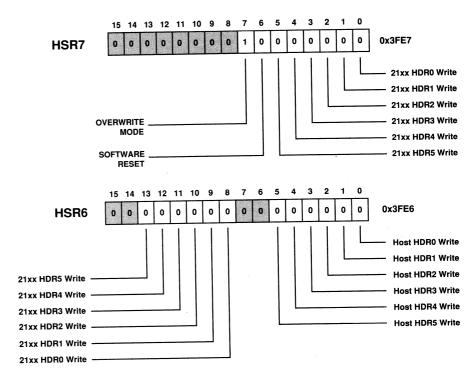

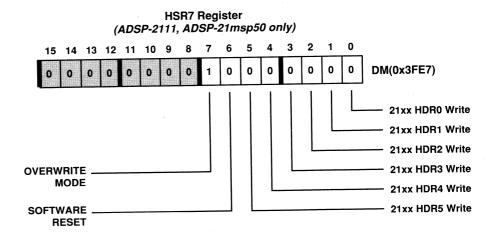

| 7.4.3   | HDR O      | verwrite Mode                               | 143             |

| 7.4.4   | Software   | e Reset                                     | 143             |

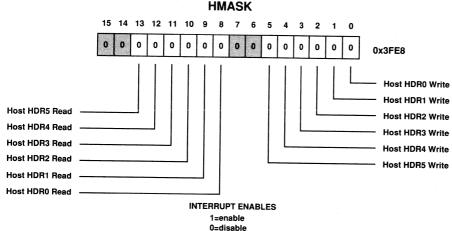

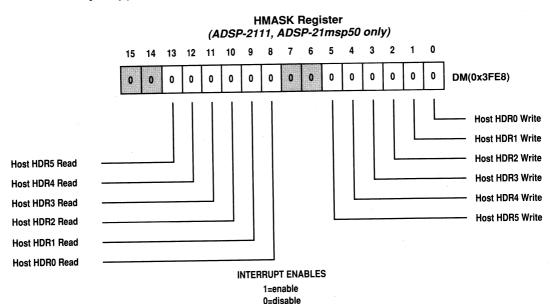

| 7.5     | HIP INTER  | RUPTS                                       | 144             |

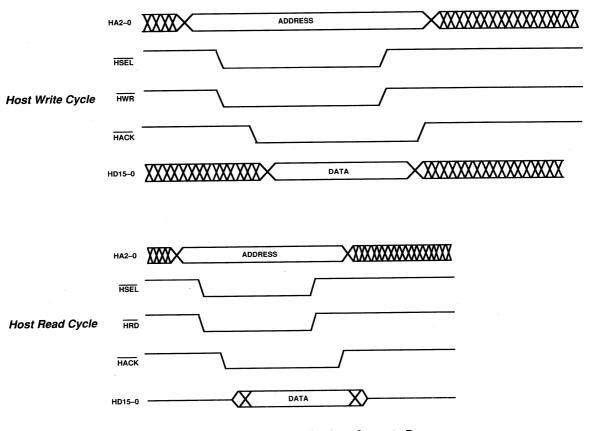

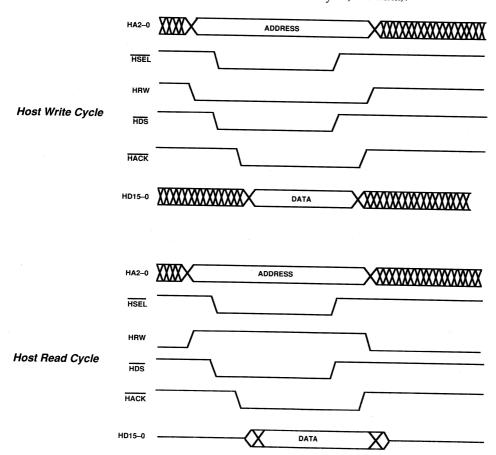

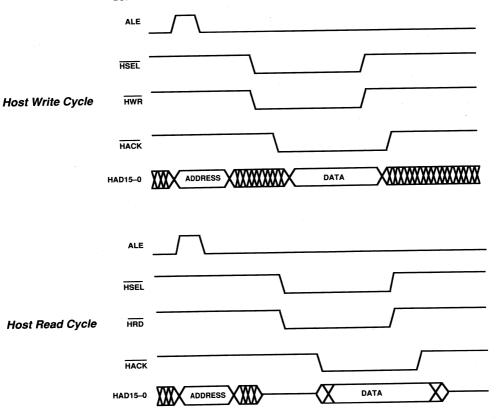

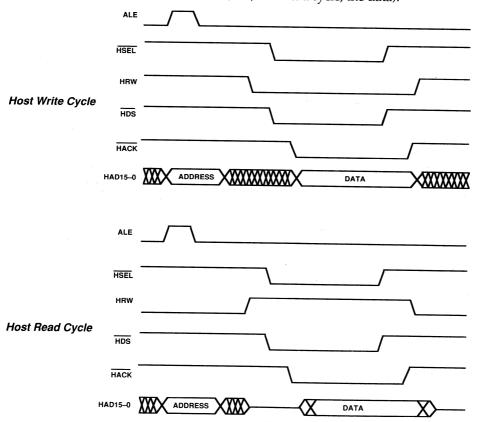

| 7.6     | HOST INTI  | ERFACE TIMING                               | 1 <del>44</del> |

| 7.7     | BOOT LOA   | DING THROUGH THE HIP                        | 143             |

|         | 2001 2011  | ENVE TIMOCOTI THE III                       | 150             |

| CHAP    | TER 8      | ANALOG INTERFACE (ADSP-21msp50A)            |                 |

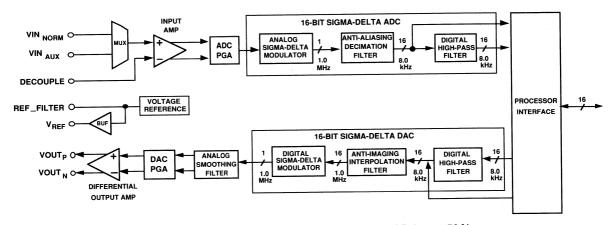

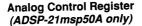

| 8.1     | OVERVIEW   | <i>I</i>                                    | 153             |

| 8.2     | A/D CONV   | /ERSION                                     | 154             |

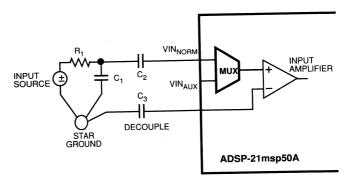

| 8.2.1   | Analog I   | Input Amplifiers                            | 154             |

| 8.2.2   | ADC        | 1                                           | 155             |

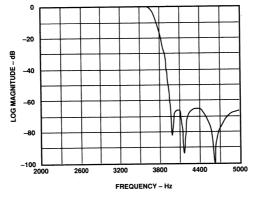

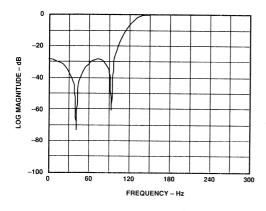

| 8.2.2.1 | Deci       | mation Filter                               | 156             |

| 8.2.2.2 | High       | Pass Filter                                 | 157             |

| 8.3     | D/A CONV   | ERSION                                      | . 158           |

| 8.3.1   | DAC        | ***************************************     | 158             |

| 8.3.1.1 | High       | Pass Filter                                 | 158             |

| 8.3.1.2 | Inter      | polation Filter                             | 159             |

| 8.3.1.3 | Anal       | og Smoothing Filter & Programmable Gain Amp | . 160           |

| 8.3.2   | Differen   | tial Output Amplifier                       | 160             |

| 8.4     | OPERATIN   | GTHE ANALOG INTERFACE                       | 141             |

| 8.4.1   | Memory     | -Mapped Control Registers                   | 161             |

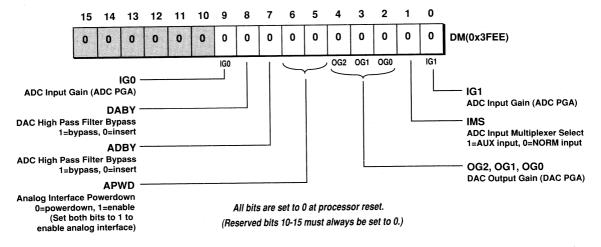

| 8.4.1.1 | Anai       | og Control Register                         | 161             |

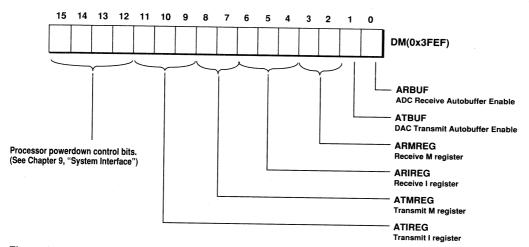

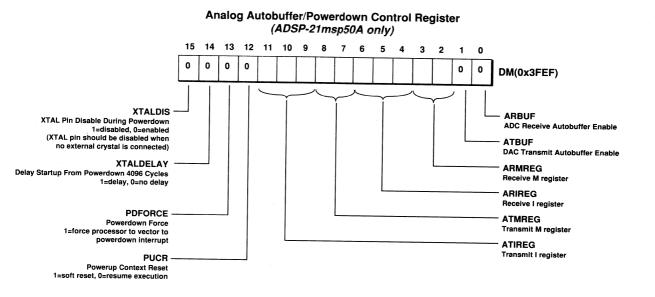

| 8.4.1.2 | Anaid      | og Autobuffer/Powerdown Register            | 162             |

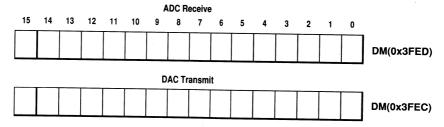

| 8.4.2   | Memory     | -Mapped Data Registers                      | 163             |

| 8.4.3   | ADC&I      | JAC Interrupts                              | 163             |

| 8.4.3.1 | Auto       | buffering Disabled                          | 164             |

| 8.4.3.2 | Auto       | bunering chapied                            | 165             |

| 3.5     | CINCUIT DI | ESIGN CONSIDERATIONS                        | 168             |

| 3.5.1   | Analog S   | ignal Input                                 | .168            |

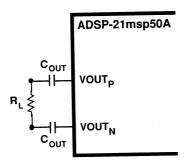

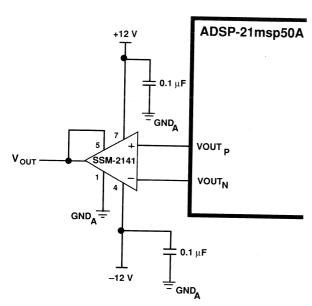

| 3.5.2   | Analog S   | ignal Output                                | 170             |

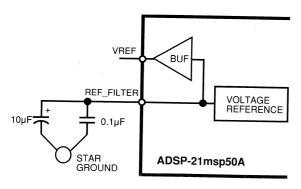

| 3.5.3   | Voltage l  | Reference Filter Capacitance                | 171             |

| CHAPT   | TER 9    | SYSTEM INTERFACE                                    |                 |

|---------|----------|-----------------------------------------------------|-----------------|

| 9.1     | OVERVIE  | W                                                   | 173             |

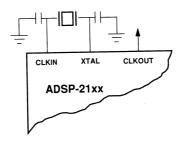

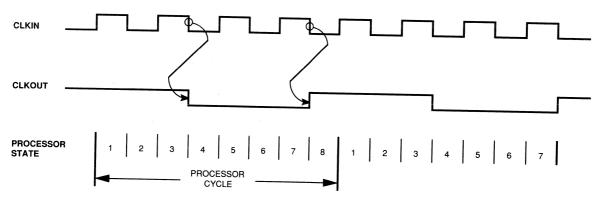

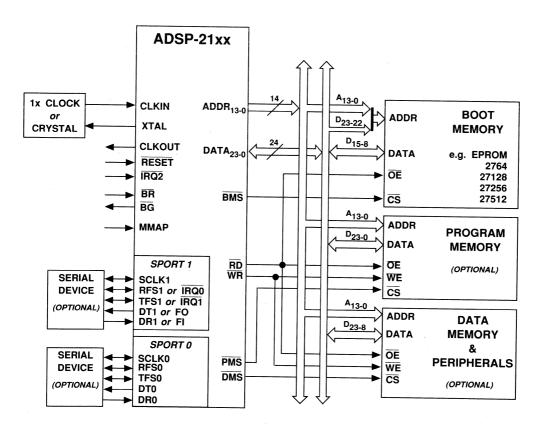

| 9.2     | CLOCKS   | GNALS                                               | 173             |

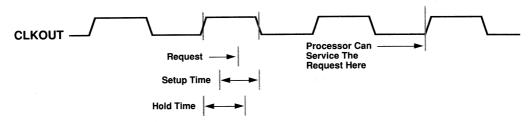

| 9.2.1   | Synchi   | onization Delay                                     | 175             |

| 9.2.2   | 1x Fred  | quency Clock Considerations                         | 175             |

| 9.3     | RESET    | increy Court I am I a | 176             |

| 9.3.1   | Reset (  | On All Family Processors (Except ADSP-2100)         | 176             |

| 9.3.2   | Reset (  | n ADSP-2100 Processor                               | 177             |

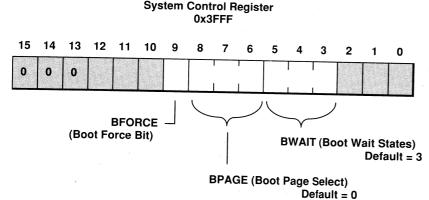

| 9.4     | SOFTWA   | RE-FORCED REBOOTING                                 | 177             |

| 9.5     | EXTERNA  | AL INTERRUPTS                                       | 182             |

| 9.5.1   | Interri  | npt Sensitivity                                     | 183             |

| 9.6     | FLAC PIN | JS                                                  | 184             |

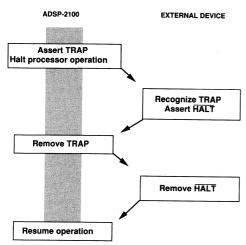

| 9.7     | HAIT&    | ГR AP (ADSP-2100 ONLY)                              | 184             |

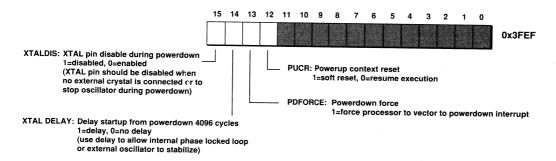

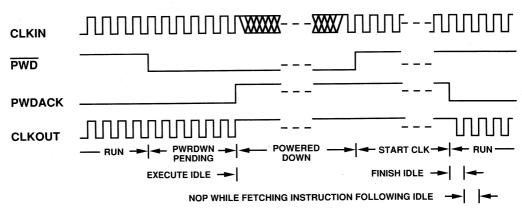

| 9.8     | POWERD   | OWN (ADSP-21MSP5X ONLY)                             | 186             |

| 9.8.1   | Power    | down Control                                        | 186             |

| 9.8.2   | Enteri   | ng Powerdown                                        | 187             |

| 9.8.3   | Exiting  | Powerdown                                           | 188             |

| 9.8.3.1 | En       | ding Powerdown With The PWD Pin                     | 188             |

| 9.8.3.2 | En       | ding Powerdown With The RESET Pin                   | 189             |

| 9.8.4   | Start-ı  | up Time After Powerdown                             | 189             |

| 9.8.4.1 | Sy       | stems Using An External TTL/CMOS Clock              | 100             |

| 9.8.4.2 | Sy       | stems Using A Crystal/Internal Oscillator           | 101             |

| 9.8.5   | Opera    | tion During Powerdown                               | 101             |

| 9.8.5.1 | Ar       | alog Interface                                      | 191<br>102      |

| 9.8.5.2 | SP       | ORTS                                                | 102             |

| 9.8.5.3 | HI       | P During Powerdown                                  | 193<br>104      |

| 9.8.5.4 | lni      | errupts And Flags                                   | 1 / 4           |

| 9.8.6   | Cond     | tions For Lowest Power Consumption                  | 19 <del>4</del> |

| 9.8.7   | PWD.     | ACK Pin                                             | 107             |

| 9.8.8   | Using    | Powerdown As A Non-Maskable Interrupt               | 17/             |

|         |          |                                                     |                 |

| CHAF    | TER 10   | MEMORY INTERFACE                                    |                 |

|         |          |                                                     | 400             |

| 10.1    | OVERVI   | EW                                                  | 199             |

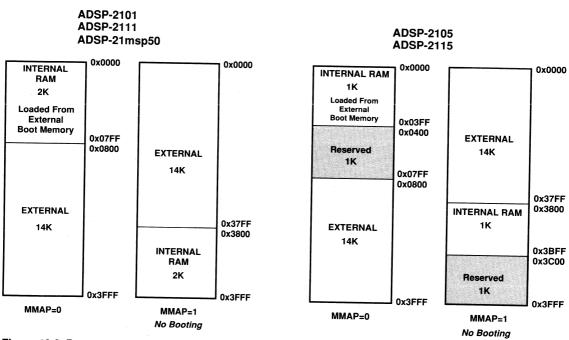

| 10.2    | A DSP-21 | 01. ADSP-2105, ADSP-2111, & ADSP-21MSP50            | 199             |

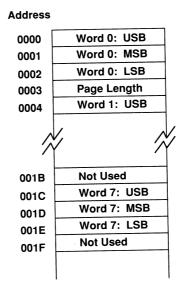

| 10.2.1  | Boot 1   | Memory Interface                                    | 200             |

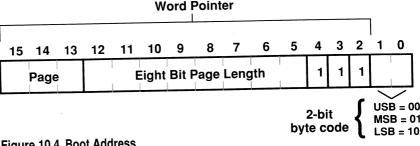

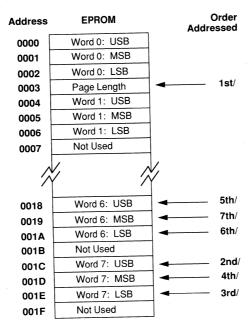

| 10.2.1. | 1 Ba     | oot Pages                                           | 202             |

| 10.2.1. | 2 Pc     | owerup Boot And Software Reboot                     | ZU3             |

| 10.2.1. | .3 Bo    | oot Memory Access                                   | 20d             |

| 10.2.1  | 4 Bo     | oot Loading Sequence                                | 204             |

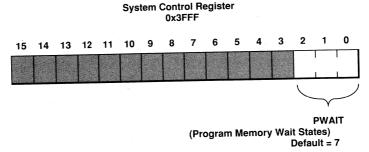

| 10.2.2   | Program Memory Interface               | 205 |

|----------|----------------------------------------|-----|

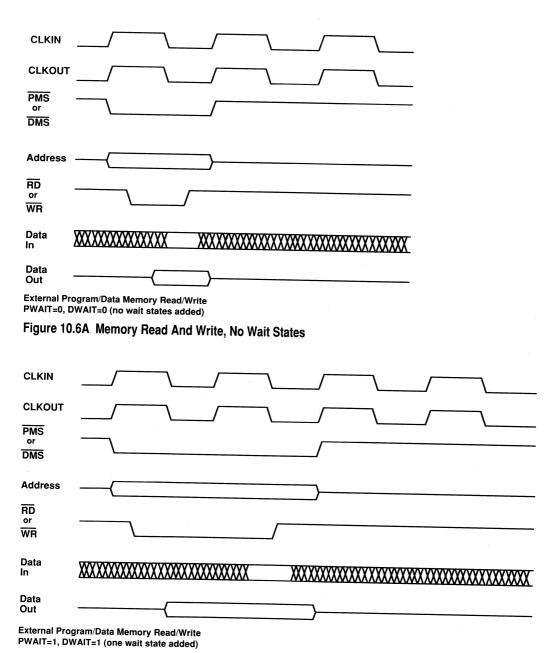

| 10.2.2.1 | Program Memory Read/Write              | 206 |

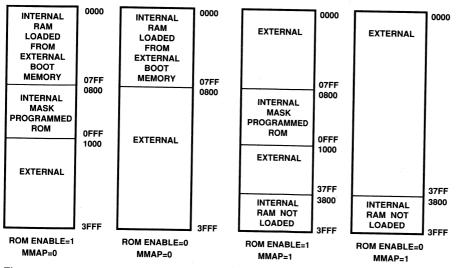

| 10.2.2.2 | Program Memory Map                     | 208 |

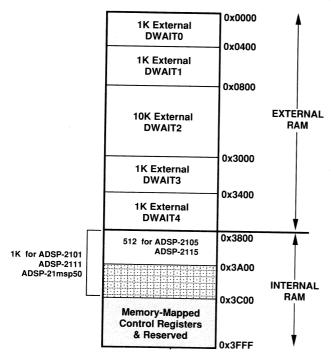

| 10.2.3   | Data Memory Interface                  | 210 |

| 10.2.3.1 | Data Memory Read/Write                 | 210 |

| 10.2.3.2 | Data Memory Map                        | 211 |

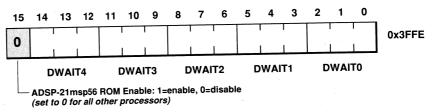

| 10.2.3.3 | Parallel And Memory-Mapped Peripherals | 212 |

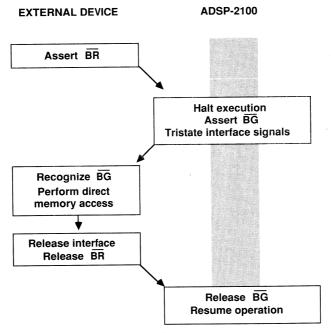

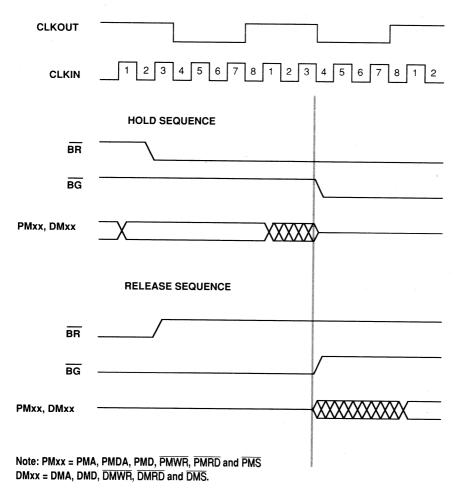

| 10.2.4   | Bus Request/Grant                      | 212 |

| 10.2.5   | Memory Interface Summary               | 214 |

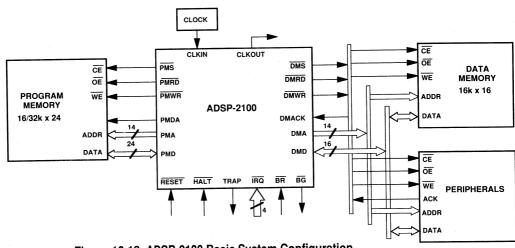

| 10.3 A   | ADSP-2100 PROCESSOR                    | 214 |

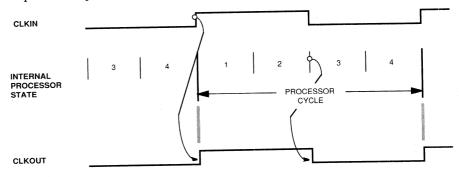

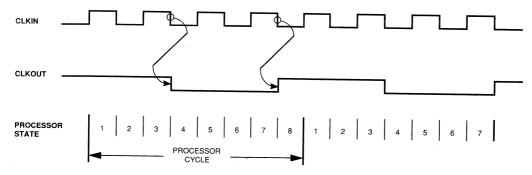

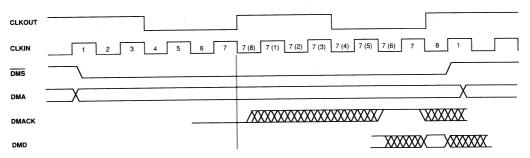

| 10.3.1   | Clock Signals & Processor States       | 216 |

| 10.3.2   | Synchronization Delay                  | 216 |

| 10.3.3   | Program Memory Interface               | 217 |

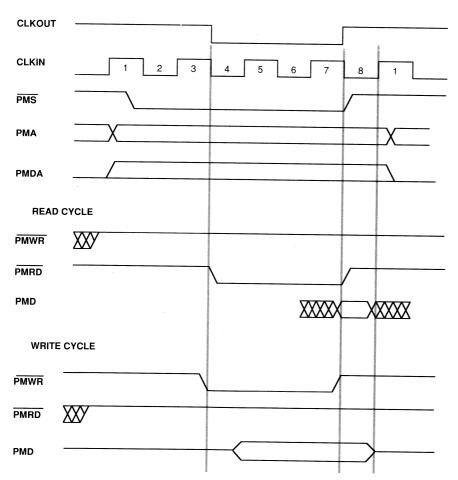

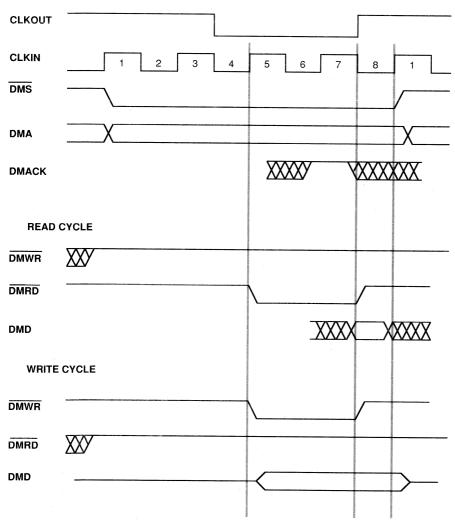

| 10.3.3.1 | Program Memory Read Cycle              | 218 |

| 10.3.3.2 | Program Memory Write Cycle             | 218 |

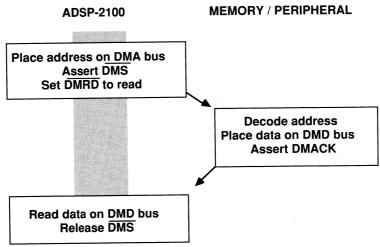

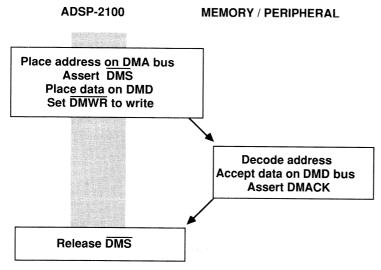

| 10.3.4   | Data Memory Interface                  | 220 |

| 10.3.4.1 | Data Memory Read Cycle                 | 222 |

| 10.3.4.2 | Data Memory Write Cycle                | 223 |

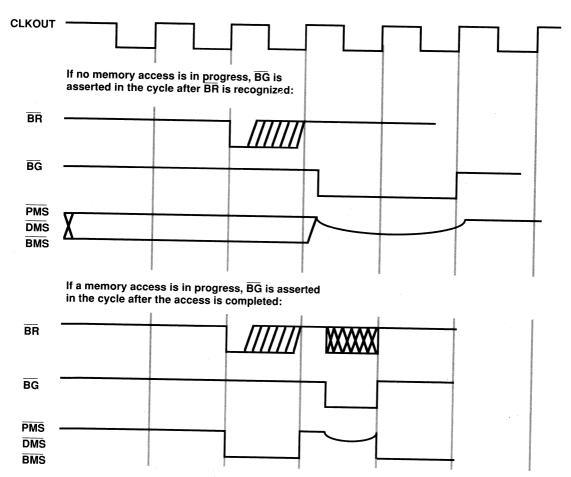

| 10.3.5   | Bus Request/Grant                      | 223 |

|          |                                        |     |

|          |                                        |     |

| CHAPTE   | R 11 PROGRAMMING MODEL                 |     |

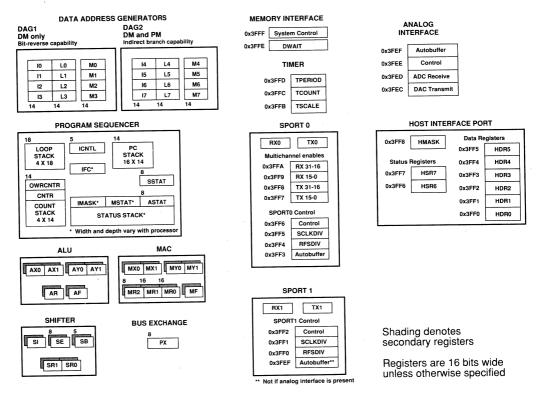

| 11.1 C   | VERVIEW                                | 227 |

| 11.1.1   | Data Address Generators                | 22/ |

| 11.1.2   | Program Sequencer                      | 229 |

| 11.1.2.1 | Interrupts                             | 220 |

| 11.1.2.2 | Loop Counts                            | 220 |

| 11.1.2.3 | Status And Mode Bits                   | 230 |

| 11.1.2.4 | Stacks                                 | 220 |

| 11.1.3   | Computational Units                    | 231 |

| 11.1.4   | Bus Exchange                           | 237 |

| 11.1.5   | Timer                                  | 737 |

| 11.1.6   | Serial Ports                           | 232 |

| 11.1.7   | Memory Interface And SPORT Enables     | 732 |

| 11.1.8   | Host Interface                         | 233 |

| 11.1.9   | Analog Interface                       | 233 |

|          |                                        | 233 |

| СНАРТ   | TER 12         | INSTRUCTION SET REFERENCE                 |     |

|---------|----------------|-------------------------------------------|-----|

| 12.1    | OUICK LIS      | ST OF INSTRUCTIONS                        | 235 |

| 12.2    | OVERVIEV       | N                                         | 236 |

| 12.3    | <b>INSTRUC</b> | FION TYPES & NOTATION CONVENTIONS .       | 237 |

| 12.4    | <b>MULTIFU</b> | NCTION INSTRUCTIONS                       | 238 |

| 12.4.1  | ALU/N          | MAC With Data & Program Memory Read       | 238 |

| 12.4.2  | Data &         | Program Memory Read                       | 240 |

| 12.4.3  | Compu          | itation With Memory Read                  | 240 |

| 12.4.4  | Compu          | itation With Memory Write                 | 240 |

| 12.4.5  | Compu          | itation With Data Register Move           | 241 |

| 12.5    | ALU, MÃO       | C & SHIFTER INSTRUCTIONS                  | 243 |

| 12.5.1  | ALU G          | roup                                      | 243 |

| 12.5.2  | MAC C          | Group                                     | 244 |

| 12.5.3  | Shifter        | Group                                     | 245 |

| 12.6    | MOVE: RE       | EAD & WRITE                               | 246 |

| 12.7    | PROGRAM        | M FLOW CONTROL                            | 248 |

| 12.8    | MISCELLA       | ANEOUS INSTRUCTIONS                       | 249 |

| 12.9    | DATA STI       | RUCTURES & VARIABLES                      | 251 |

| 12.9.1  | Arrays         |                                           | 251 |

| 12.9.2  | Circula        | or Arrays/Buffers                         | 252 |

| 12.10   | INDIRECT       | LINEAR (NON-CIRCULAR) ADDRESSING.         | 253 |

| 12.10.1 |                | egisters To 0 For Non-Circular Addressing | 253 |

| 12.11   |                | ME NOTES                                  | 254 |

| 12.11.1 | ADSP-          | 2100 Extra Cycle Conditions               | 254 |

| 12.11.2 | Extra C        | Cycle Conditions For All Other Processors | 254 |

| 12.11.2 | .1 Mu          | ltiple Off-Chip Memory Accesses           | 254 |

| 12.11.2 | .2 Wa          | it States                                 | 254 |

| 12.11.2 | .3 SPC         | ORT Autobuffering                         | 255 |

| 12.12   | INSTRUC        | TION SET SYNTÄX                           | 255 |

| 12.12.1 | Punctu         | nation & Multifunction Instructions       | 255 |

| 12.12.2 | Syntax         | Notation Example                          | 256 |

| 12.12.3 | Status         | Register Notation                         | 256 |

| 12.13   | PROGRAI        | M EXAMPLE                                 | 257 |

| 12.13.1 | Examp          | ble Program: Setup Routine Discussion     | 258 |

| 12.13.2 | Examp          | ole Program: Interrupt Routine Discussion | 260 |

| ALU    | Add/Add with Carry                      | 263             |

|--------|-----------------------------------------|-----------------|

|        | Subtract X-Y/Subtract X-Y with Borrow   | 200             |

|        | Subtract Y-X/Subtract Y-X with Borrow   | 20 <del>.</del> |

|        | AND, OR, XOR                            | 266             |

|        | Pass/Clear                              | 260<br>267      |

|        | Negate                                  | 267<br>268      |

|        | NOT                                     | 260             |

|        | Absolute Value                          | 207<br>270      |

|        | Increment                               | 271             |

|        | Decrement                               | 272             |

|        | Divide                                  | 273             |

|        |                                         |                 |

| MAC    | Multiply                                | 275             |

|        | Multiply/Accumulate                     | 277             |

|        | Multiply/Subtract                       | 279             |

|        | Clear                                   | 281             |

|        | Transfer MR                             | 282             |

|        | Conditional MR Saturation               | 283             |

| OI III |                                         |                 |

| SHIFTI |                                         |                 |

|        | Arithmetic Shift                        | 284             |

|        | Logical Shift                           | 286             |

|        | Normalize                               | 288             |

|        | Derive Exponent                         | 290             |

|        | Block Exponent Adjust                   | 292             |

|        | Arithmetic Shift Immediate              | 294             |

|        | Logical Shift Immediate                 | 296             |

| MOVE   | Pagistar Mayo                           |                 |

| WIOVE  | Register Move                           | 298             |

|        | Load Register Immediate                 | 299             |

|        | Data Memory Read (Direct Address)       | 301             |

|        | Data Memory Read (Indirect Address)     | 302             |

|        | Program Memory Read (Indirect Address)  | 303             |

|        | Data Memory Write (Direct Address)      | 304             |

|        | Data Memory Write (Indirect Address)    | 305             |

|        | Program Memory Write (Indirect Address) | 307             |

| PROGR  | RAM FLOW                                |                 |

|        | JUMP                                    | 308             |

|        | CALL                                    | 300             |

|        | JUMP or CALL on Flag In Pin             | 310             |

|        | Modify Flag Out Pin                     | 311             |

|        | Return From Subroutine (RTS)            | 217             |

|        | Return From Interrupt (RTI)             | 312             |

|        | Do Until                                                                     | 314         |

|--------|------------------------------------------------------------------------------|-------------|

|        | IDLE                                                                         | 310<br>217  |

|        | TRAP (ADSP-2100 only)                                                        | 317         |

| MISC   | Stack Control                                                                | 318         |

|        | Mode Control                                                                 | 320         |

|        | Modify Address Register                                                      | 322         |

|        | NOP                                                                          | 323         |

| MULT   | IFUNCTION                                                                    |             |

|        | AIII/MAC/SHIFT Operation with Memory Read                                    | 324         |

|        | AIII/MAC/SHIFT Operation with Register to Register Move.                     | 328         |

|        | ALII/MAC/SHIFT Operation with Memory Write                                   | 331         |

|        | Data & Program Memory Read                                                   | 335         |

|        | Data & Program Memory Read ALU/MAC Operation with Data & Program Memory Read | 336         |

| CITAD  | TER 13 HARDWARE EXAMPLES                                                     |             |

| CHAP   |                                                                              |             |

| 13.1   | OVERVIEW                                                                     | .339        |

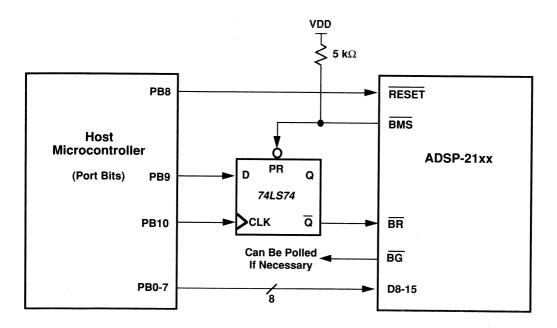

| 13.2   | BOOT LOADING FROM HOST USING BUS REQUEST                                     | .340        |

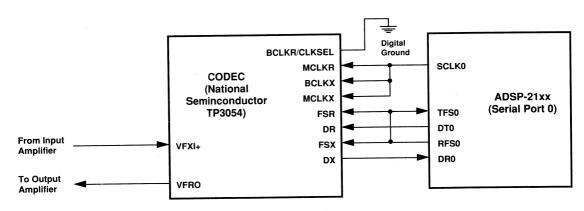

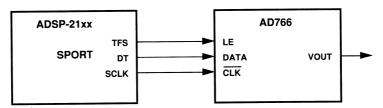

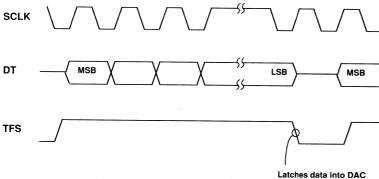

| 13.3   | SERIAL PORT TO CODEC INTERFACE                                               | .343        |

| 13.4   | SERIAL PORT TO DAC INTERFACE                                                 | .346        |

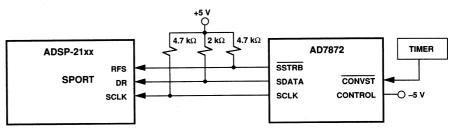

| 13.5   | SERIAL PORT TO ADC INTERFACE                                                 | .348        |

| 13.6   | SERIAL PORT TO SERIAL PORT INTERFACE                                         | .330        |

| 13.7   | 80C51 INTERFACE TO HOST INTERFACE PORT                                       | .331        |

| CITAT  | TER 14 SOFTWARE EXAMPLES                                                     |             |

| СПАГ   |                                                                              |             |

| 14.1   | OVERVIEW                                                                     | .353        |

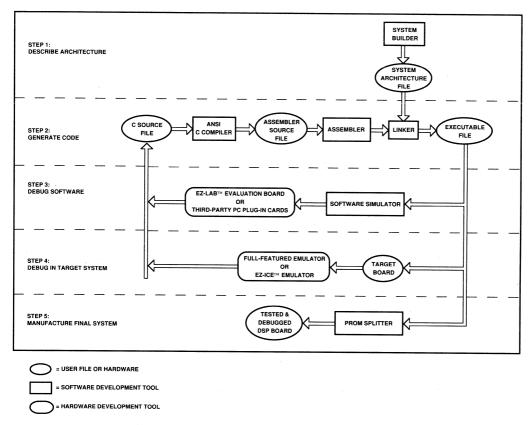

| 14.2   | SYSTEM DEVELOPMENT PROCESS                                                   | .354        |

| 14.3   | SINGLE-PRECISION FIR TRANSVERSAL FILTER                                      | .356        |

| 14.4   | CASCADED BIQUAD IIR FILTER                                                   | <i>3</i> 28 |

| 14.5   | SINE APPROXIMATION                                                           | 339         |

| 14.6   | SINGLE-PRECISION MATRIX MULTIPLY                                             | 301         |

| 14.7   | RADIX-2 DECIMATION-IN-TIME FFT                                               |             |

| 14.7.1 | Main Module                                                                  | 303<br>345  |

| 14.7.2 | DIT FFT Subroutine                                                           | 505<br>170  |

| 14.7.3 | Bit-Reverse Subroutine                                                       | <i></i> 770 |

| 14.7.4 | Block Floating-Point Scaling Subroutine                                      |             |

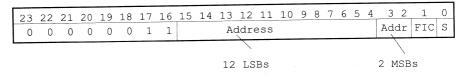

| APPE       | NDIX A              | INSTRUCTION CODING                                  |            |

|------------|---------------------|-----------------------------------------------------|------------|

| A.1<br>A.2 | OPCODES<br>ABBREVIA | ATION CODING                                        | 373<br>378 |

| APPE       | NDIX B              | DIVISION EXCEPTIONS                                 |            |

| B.1        | DIVISION            | FUNDAMENTALS                                        | 207        |

| B.1.1      | Signed              | Division                                            | 387<br>207 |

| B.1.2      | Unsign              | ed Division                                         | 38/        |

| B.1.3      | Output              | ed DivisionFormats                                  | 300        |

| B.1.4      | Integer             | Division                                            | 389        |

| B.2        | ERROR CO            | ONDITIONS                                           | 389        |

| B.2.1      | Negativ             | ve Divisor Error                                    | 389        |

| B.2.2      | Unsign              | ed Division Error                                   | 390        |

| B.3        | SOFTWAR             | ve Divisor Error<br>ed Division Error<br>E SOLUTION | 390        |

| APPE       | NDIX C              | NUMERIC FORMATS                                     |            |

| C.1        | OVERVIEW            | V                                                   | 395        |

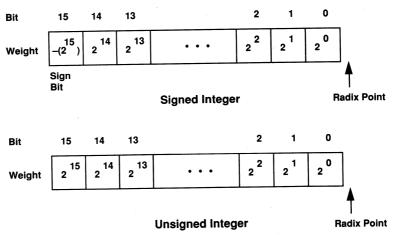

| C.2        | UNSIGNE             | D OR SIGNED: TWOS-COMPLEMENT FORMAT                 | 395        |

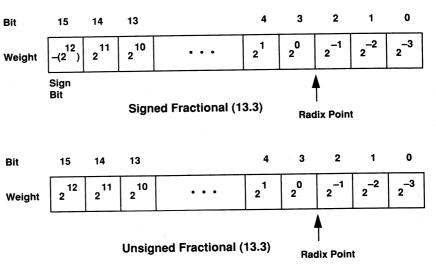

| C.3        | INTEGER (           | OR FRACTIONAL                                       | 395        |

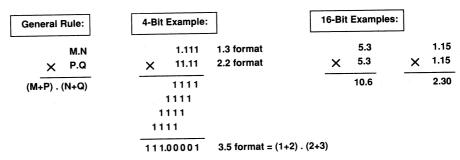

| C.4        | BINARY M            | IULTIPLICATION                                      | 307        |

| C.4.1      | Fraction            | nal Mode And Integer Mode                           | 398        |

| C.5        | BLOCK FL            | nal Mode And Integer Mode<br>OATING-POINT FORMAT    | 399        |

|            |                     |                                                     |            |

| APPE       | NDIX D              | PIN DESCRIPTIONS                                    |            |

| D.1        | OVERVIEW            | V                                                   | 101        |

| D.2        | ADSP-2100           | PIN DESCRIPTIONS                                    | 401        |

| D.3        | ADSP-2101           | / ADSP-2115 PINI DESCRIPTIONS                       | 400        |

| D.4        | ADSP-2105           | PIN DESCRIPTIONS                                    | 402        |

| D.5        | ADSP-2111           | PIN DESCRIPTIONS                                    | 403        |

| D.6        | ADSP-21ms           | sp50 PIN DESCRIPTIONS                               | 405        |

|            |                     |                                                     |            |

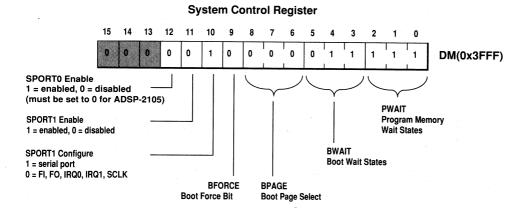

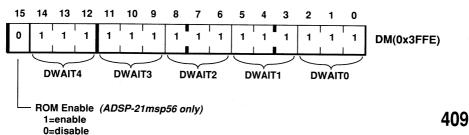

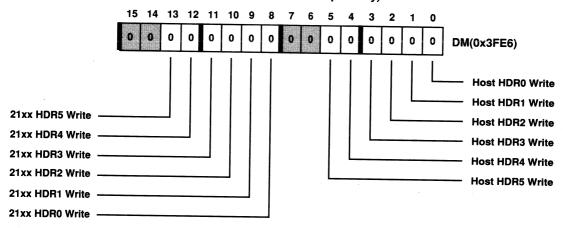

| APPENDIX E    | CONTROL/STATUS REGISTERS                    | 409        |

|---------------|---------------------------------------------|------------|

| REVISIONS FRO | OM 1ST EDITION                              | 423        |

| TOPPCS TOPPCS | TACK Special Instructions TACK Restrictions | 431<br>433 |

| INDEX         |                                             | 435        |

#### **Preface**

This book is intended to serve primarily as a guide and reference for the design engineer. As the title suggests, it is a technical manual which will find its home both on the office bookshelf and laboratory workbench. For the non-technical reader, the book can also provide an overall understanding of what DSP is all about. Other professionals who will find this text informative include industry analysts, marketing engineers, and general technologists.

The topics addressed include, but are not limited to, architectural features of the DSP processor family that facilitate signal processing and ease the task of programming. The primary message delivered in the manual's introduction is that digital signal processing is gaining acceptance as a mainstream technology. The first three chapters, detailing computation units, program controller, and data transfers, are the core of this book. These are derived from previous editions of the *ADSP-2100*, *ADSP-2101*, and *ADSP-2111 User's Manuals*. Later portions of the book discuss system and memory interfacing considerations and provide a programmer's model.

To serve as a technical reference, the *ADSP-2100 Family User's Manual* includes a complete instruction set reference and appendix of pin descriptions. Mathematical considerations are covered in the appendices for division exceptions and numeric formats as well as the computation units chapter. Finally, the hexadecimal bit patterns of processor control registers, so difficult to remember for any digital designer, are "spelled out" in a highly visual way at the very back of the book where she or he can quickly find them.

The ADSP-2100 Family consists of the following processors at the time of publication of this manual: ADSP-2100A, ADSP-2101, ADSP-2103, ADSP-2105, ADSP-2115, ADSP-2111, and ADSP-21msp50A. Note that the ADSP-2100A offers a slightly different architecture than the other family processors, all of which contain on-chip memory. As new variants are added to the product line, this manual can be used as a reference for the new devices. For current information and product literature, contact Analog Devices DSP Customer Support at (617) 461-3881.

#### Acknowledgements

The substance of this text was provided by many, if not all, of the individuals of Analog Devices' DSP Division. Primary contributors included members of Technical Publications, Applications Engineering, and Design Engineering. Adele Hastings provided all drawings and layout as well as editing for all chapters of this book.

Special thanks also to Amy Mar, Jim McQuaid, Dan Sheingold, and Karen Gettman.

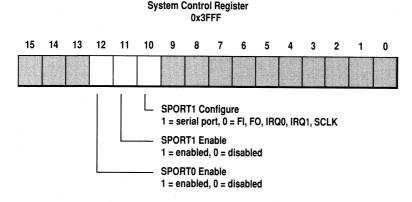

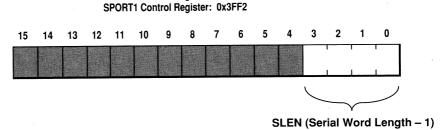

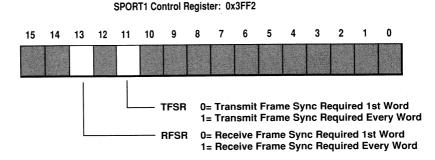

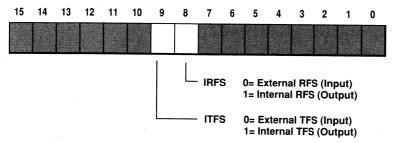

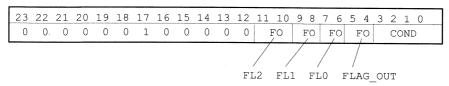

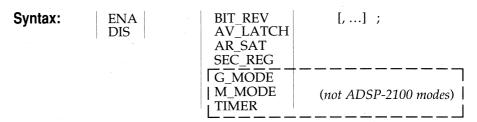

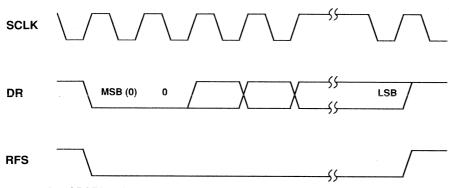

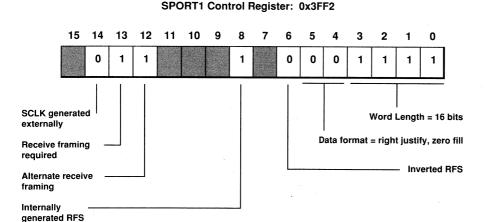

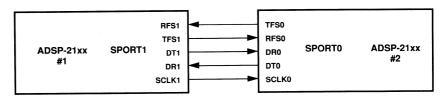

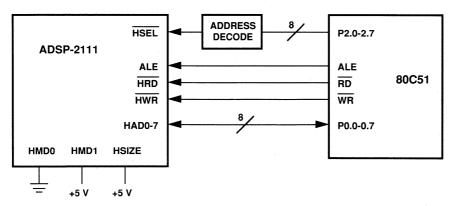

#### 1.1 OVERVIEW